Shift Register (HDLBits)

SISO Shift Registers with Synchronous Active-Low Reset

📌 Question

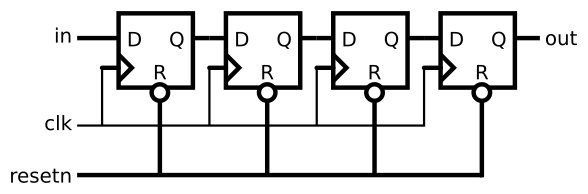

Implement the following circuit:

🧑💻 Code Example

RTL Code

module top_module #(

parameter WIDTH = 4

) (

input wire clk,

input wire resetn, // synchronous reset

input wire in,

output wire out);

reg [WIDTH-1:0] Q;

assign out = Q[WIDTH-1];

always @(posedge clk) begin

if (~resetn)

Q <= {WIDTH{1'b0}};

else

Q <= {Q[WIDTH-2:0], in};

end

endmodule

Testbench Code

`timescale 1ns/1ps

module tb_top_module;

reg clk;

reg resetn;

reg in;

wire out;

top_module dut (

.clk(clk),

.resetn(resetn),

.in(in),

.out(out)

);

initial begin

resetn = 1;

clk = 0;

in = 0;

forever #5 clk = ~clk;

end

initial begin

$dumpfile("tb_top_module.vcd");

$dumpvars(0, tb_top_module);

// Initialize

#10

resetn = 0;

#10;

resetn = 1;

in = 1;

#10;

in = 0;

#50;

in = 1;

#10;

in = 0;

// Reset again

resetn = 0;

#10;

resetn = 1;

#30;

in = 1;

#10;

in = 0;

#30;

$finish;

end

initial begin

$monitor("Time=%0t resetn=%b out=%b", $time, resetn, out);

end

endmodule

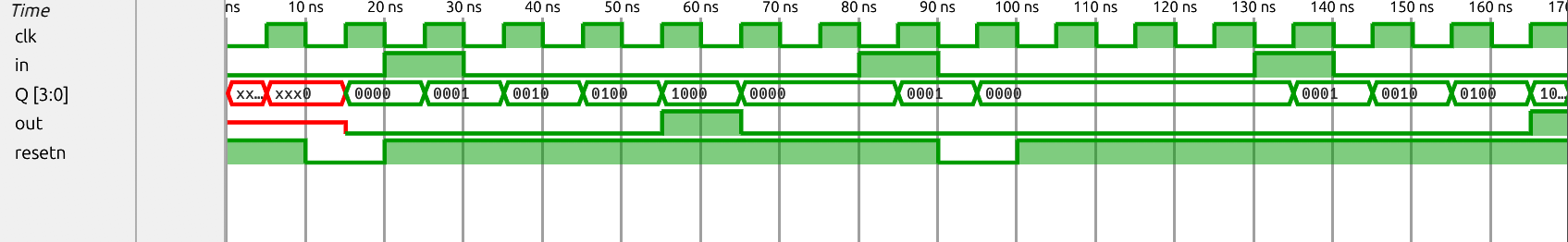

🔬 Results

Simulation Waveform

Synthesis RTL-level Schematic

Synthesis Gate-level Schematic